2018년 11월 26일

메모리 인터리빙 (Memory Interleaving)

1. 병렬 메모리 접근, 메모리 인터리빙

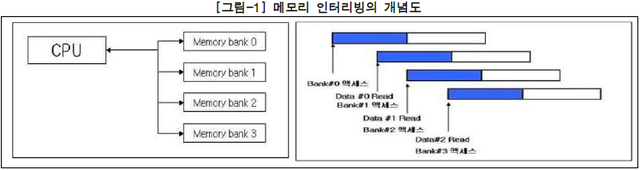

(1) 메모리 인터리빙의 개념

- 메모리 접근 시간을 최소화하기 위해 여러 모듈로 나눈 메모리에 동시 접근하는 기법

(2) 메모리 인터리빙 개념도

- CPU가 Bank#0에 Address#0을 보냄, CPU가 Address#1을 Bank#1에 보내고 Data#0을 Bank#0에서 수신하는 동작을 반복하여 한 개의 Bank가 Refresh하는 동안 다른 Bank Access

2. 메모리 인터리빙 활용 방식

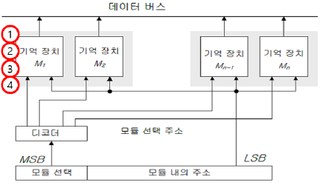

(1) 상위 인터리빙 방식 설명

| – 모듈 들에 순차 지정 방식 – 상위 비트: 모듈 선택 신호 – 하위 비트: 기억 장소 선택 (장) 에러 시 한 모듈만 영향 (단) 같은 모듈 동시접근 어려움 |

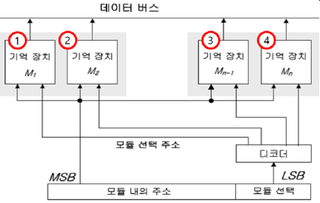

(2) 하위 인터리빙 방식 설명

| – 기억장치 주소가 모듈 단위 – 하위 비트: 모듈 선택 신호 – 상위 비트: 모듈 내 기억 장소 (장) 다수 모듈 동시 동작 (단) 구조 변경 불가, 에러전파 |

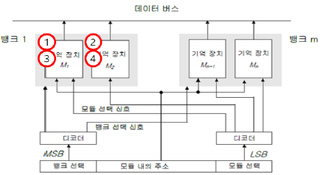

(3) 혼합 인터리빙 방식 설명

| – 기억장치 모듈을 뱅크로 그룹화 – 뱅크 선택 시 상위 인터리빙 – 뱅크 내 모듈 간 하위 인터리빙 (장) 상/하위 인터리빙 단점 해결 (단) 구현 복잡, 어려움 |

3. 메모리 인터리빙 액세스 활용 방식

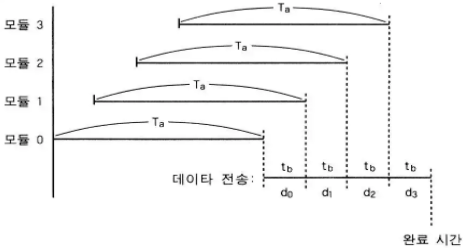

(1) C-Access 방식 (상위 인터리빙 방식)

| 구분 | 설명 |

|---|---|

| 시간 그래프 |  |

| 액세스 시간 | ※ Access 시간: T = Ta + (M x tb) (Ta = 기억장치 접근 시간, tb = 버스 클럭 주기, M = 기억장치 모듈 수) |

| 특징 | – 프로세서-기억장치 간 버스 통해 순차적 도착 – 모듈 접근 중첩되지만 실제 접근 시 딜레이 |

| 장점 | – 별도 장치 없이 단순한 구현 |

| 단점 | – 모듈 전송 과정 버스 경합으로 도착 불가 가능 – 도착불가 시 동시성 저하, 데이터 연속전송불가 |

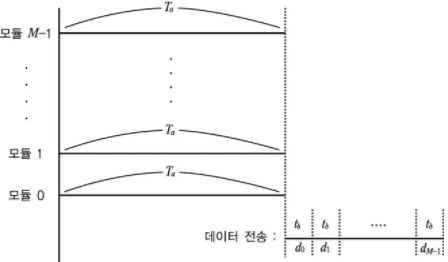

(2) S-Access 방식 (하위 인터리빙 방식)

| 구분 | 설명 |

|---|---|

| 시간 그래프 |  |

| 액세스 시간 | ※ Access 시간: T = Ta + (M x tb) (Ta = 기억장치 접근 시간, tb = 버스 클럭 주기, M = 기억장치 모듈 수) |

| 특징 | – 모든 모듈에서 읽기 동작이 동시 시작 – Read 데이터 순차적 전송 – DDR DRAM에서 적용, 파이프라인에서 사용 |

| 장점 | – 동시 Access 보장, 연속전송 (Burst Bus Mode) |

| 단점 | – 필요 Data가 동시 Access 수 초과 시 비효율 |

- S-Access 방식이 읽기 동작의 동시성 확보 통한 높은 성능 제공

4. 메모리 인터리빙 활용사례

| 활용사례 | 활용 방식 | 설명 |

|---|---|---|

| Pipeline | – 하위 인터리빙 – S-Access | – 다수 CPU 활용 시 메모리 병렬 접근 |

| SPOF 극복 | – 상위, 혼합 – C-Access | – 메모리 순차접근으로 에러 전파 영향 없음 |

| DDR DRAM | – 하위 인터리빙 – S-Access | – SDRAM Refresh – Read 동시성 성능보장 |

- 인터리빙은 캐시 기억장치 Line 단위 Burst 전송 및 고속 DMA Burst 전송 시 사용