2018년 11월 19일

폰노이만 아키텍처

1. 현대 컴퓨터의 기반 구조, 폰노이만 아키텍처

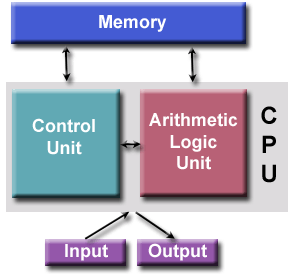

| 개념도 | 개념 |

|---|---|

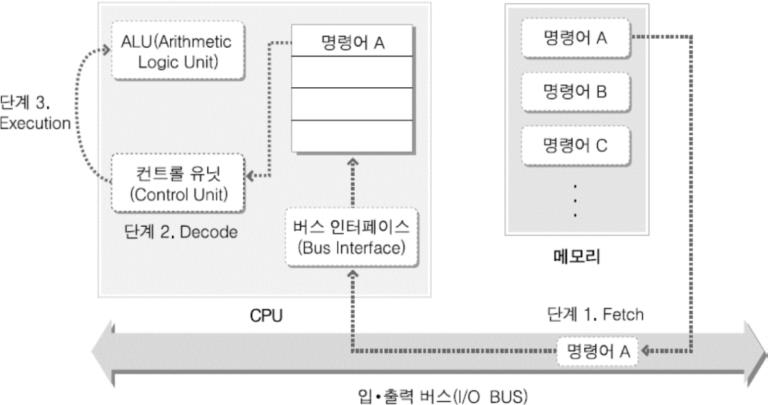

| – 메모리에서 명령어를 인출, CU에서 해석, ALU에서 연산하여 저장하는 현대 컴퓨터 구조의 기반 아키텍처 |

2. 폰노이만 아키텍처 구성도 및 구성요소

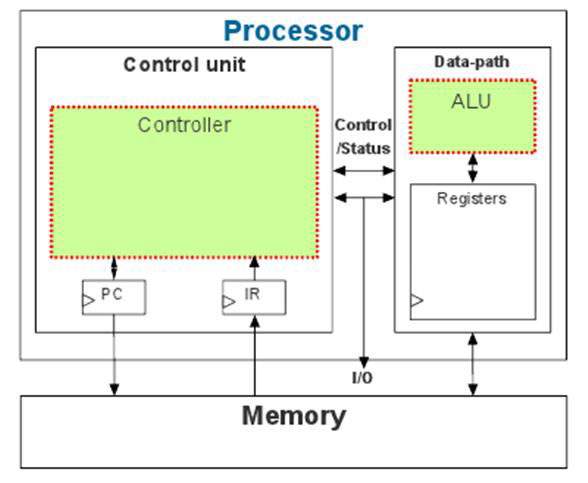

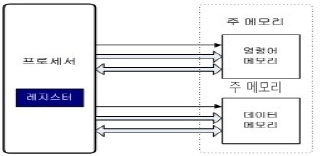

(1) 폰노이만 아키텍처의 구성도

|  |

- CPU는 한 번에 하나의 명령어만 실행 가능(SISD)

(2) 폰노이만 아키텍처의 구성요소

| 구분 | 구성요소 | 설명 |

|---|---|---|

| CPU | ALU | – 산술 논리 연산 기능 주요 장치 |

| CU | – 명령어 해독(Decode), 메모리제어 | |

| Register | – CPU동작 관련 데이터 임시저장 | |

| BUS | 주소 버스 | – 외부 발생 주소 정보 전송 신호선 |

| 데이터 버스 | – 기억장치-I/O장치 전송, x86_64bit | |

| 제어 버스 | – 시스템 내 장치에 동작 신호선 | |

| 메모리 | 주기억장치 | – CPU근접 기억장치, 고속, 휘발성 |

| 보조기억장치 | – 별도제어, 영구저장장치, 느린속도 |

- 메모리 내장 방식의 구조로 현대 컴퓨터의 근간이되는 아키텍처, 빠른속도의 CPU를 효과적으로 사용하지 못하는 단점을 개선하여 하바드 아키텍처 등장

3. 폰노이만 아키텍처와 하바드 아키텍처 비교

구분 | 폰노이만 | 하바드 |

|---|---|---|

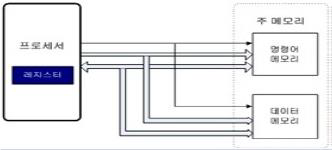

| 구성 |  |  |

| 특징 | – 메모리에 명령어, 데이터 모두 저장 | – 서로 다른 메모리에 명령어, 데이터 각저장 |

| 처리 방식 | – 특정주소지점부터 실행 – 명령어/데이터 구분없음 | – 명령어/데이터 구분기반 동시 접근 수행 가능 |

| 장점 | – 공유 메모리 사용으로 구현이 쉽고 저렴함 | – 파이프라인 기술 최적 환경(구조 해저드 해결) |

| 단점 | – 구조적 해저드 발생 – 병목 현상 발생 | – 별도 메모리 사용으로 구현비용증가/회로복잡 |

[참고]

- Wikipedia, Von Neumann architecture