2018년 11월 23일

플래시 메모리

1. 고속, 저전력, 비휘발성 저장매체, 플래시 메모리

(1) 플래시 메모리의 개념

- 기계적 동작이 없는 순수 반도체로 이루어져 빠른 속도와 전력소모가 적은 비휘발성 메모리

(2) 플래시 메모리의 특징

| 특징 | 설명 |

|---|---|

| 덮어쓰기 연산이 제한적 | – 덮어쓰기 불가능 시 기존 페이지 무효화 후 새로운 페이지에 기록 |

| 소거 연산 오버헤드 | – 무효화 페이지 재사용 위해 소거 연산을 먼저 수행하여 오버헤드 발생 |

2. 플래시 메모리 쓰기, 삭제, 읽기 과정

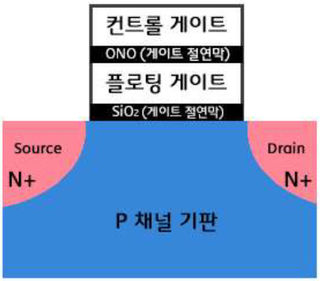

(1) 플래시 메모리 구조

| – 2층 구조 게이트 전극의 아래쪽은 플로팅 게이트, 위쪽은 컨트롤 게이트 – 데이터 저장/삭제 시 플로팅 게이트에 전자를 채우고 비우는 방식을 통해 수행 |

- 플래시 메모리는 셀 트랜지스터라고 불리는 특별한 구조의 MOS 트랜지스터에 전하 축적하여 데이터 보존

- 대표적 메모리 셀 구조는 플로팅 게이트로 2층 구조의 MOS 트랜지스터

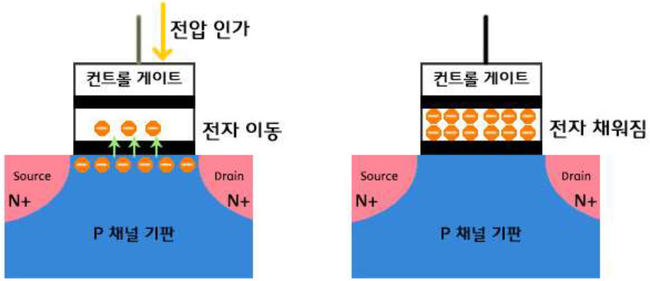

(2) 플래시 메모리 쓰기 과정

|

|

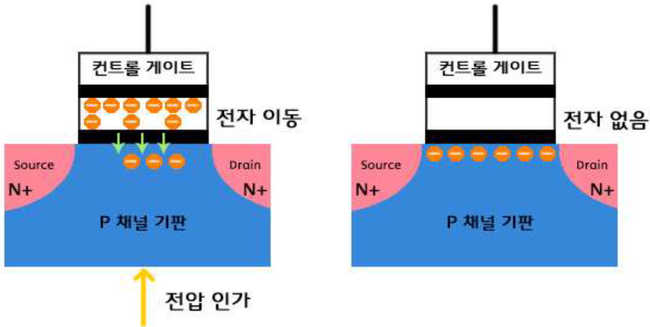

(3) 플래시 메모리 삭제 과정

|

|

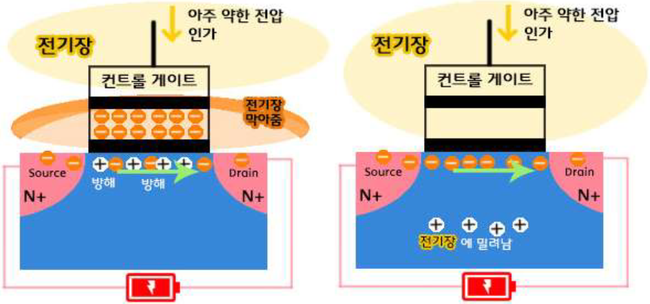

(4) 플래시 메모리 읽기 과정

|

|

3. 플래시 메모리의 유형

(1) 플래시 메모리의 회로 구조에 따른 유형

| 항목 | NAND 플래시 | NOR 플래시 |

|---|---|---|

| 특징 | – 직렬 연결 방식 – 회로 집적도 높음 | – 병렬 연결 방식 – 회로 집적도 낮음 |

| 장점 | – 프로그램 소거 빠름 | – 프로그램 바이트화 |

| 단점 | – 바이트화 불가 | – 프로그램 소거 느림 |

| 사용 | – SSD, 메모리카드 | – 핸드폰 EPROM |

| 코드실행 | – 불가능 | – 가능 |

| 블록크기 | – 8KB | – 64KB |

| 랜덤액세스 | – 불가능 | – 가능 |

| 시장주도 | – 삼성 주도 | – 인텔 주도 |

| 읽기 방식 | – Random Access | – Sequential Access |

(2) 플래시 메모리 셀 저장 용량에 따른 유형

| 항목 | SLC | MLC | TLC |

|---|---|---|---|

| 명칭 | Single Level Cell | Multi Level Cell | Triple Level Cell |

| 저장 | 1비트/소자(셀) | 2비트/소자(셀) | 3비트/소자(셀) |

| R성능 | 25㎲ | 50㎲ | ~75㎲ |

| W성능 | 200㎲~300㎲ | 600㎲~900㎲ | 900㎲~1350㎲ |

| E성능 | 1.5㎳~2㎳ | 3㎳ | ~4.5㎳ |

| 수명 | 10만회 쓰기 | 1만회 쓰기 | 1000회 내외 |

| 비용 | SLC > MLC > TLC | ||

| ECC | 오류 검출, 수정위한 ECC 복잡도 SLC < MLC < TLC | ||