2019년 1월 4일

플립플롭 (Flip-Flop)

1. 1비트 기억소자, 플립플롭 (Flip-Flop)

(1) 플립플롭의 개념

- 두 개의 안정된(bi-stable) 상태 중 하나를 가지는 클럭 펄스기반 순차논리회로 1비트 기억소자

(2) 플립플롭과 래치의 차이점 비교

| 플립플롭 (Flip-Flop) | 래치 (Latch) |

|---|---|

| – 클럭 펄스 기반 출력값 결정 순차논리회로 기억소자 | – 클럭 펄스가 입력되지 않는 순수 순차논리회로 기억소자 |

2. 플립플롭의 대표 구성도 및 메커니즘

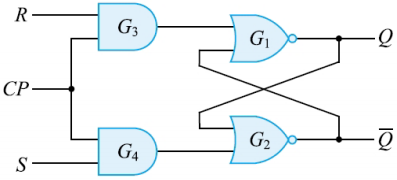

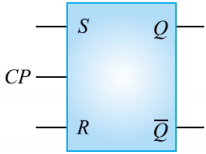

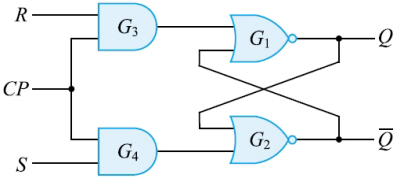

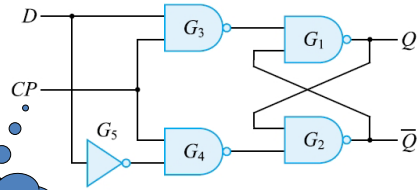

(1) 플립플롭의 회로도 및 논리기호 (SR F/F 기준)

| 회로도 | 논리기호 |

|---|---|

|  |

(2) 플립플롭의 메커니즘

| 클럭 펄스 | 메커니즘 |

|---|---|

| CP = 0 | – S, R의 입력에 관계없이 앞단 AND gate G3과 G4 출력이 항상 0이므로 플립플롭 출력 불변 |

| CP = 1 | – S와 R의 입력이 회로 후단의 NOR 게이트 G1, G2의 입력으로 전달, SR latch와 같은 동작 수행 |

3. 플립플롭의 유형 별 논리기호, 진리표, 특성표

| 구분 | 회로도 | 진리표 |

|---|---|---|

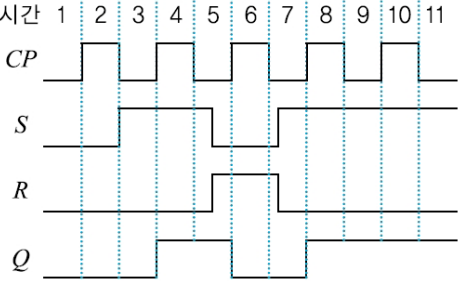

| 파형 | 특성표 | |

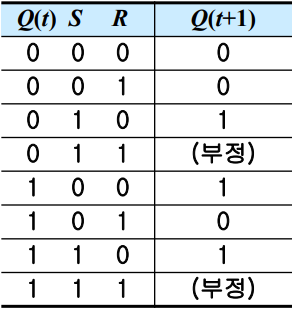

| SR F/F |  |  |

|  | |

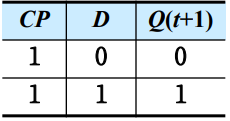

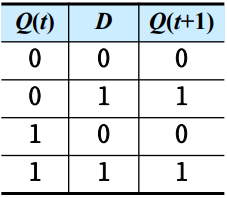

| D F/F |  |  |

|  | |

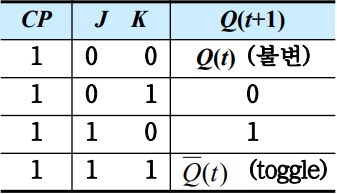

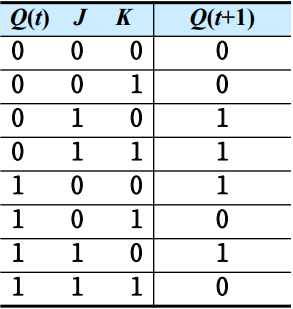

| JK F/F |  |  |

|  | |

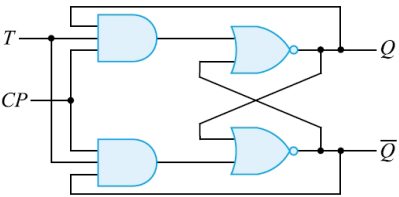

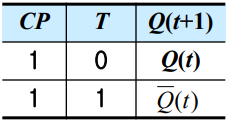

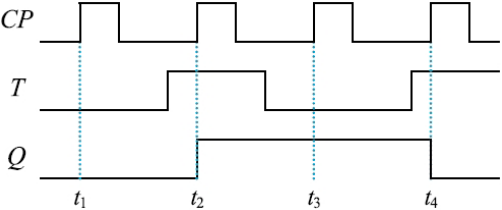

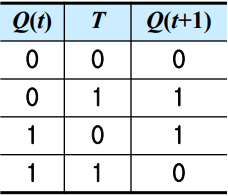

| T F/F |  |  |

|  |

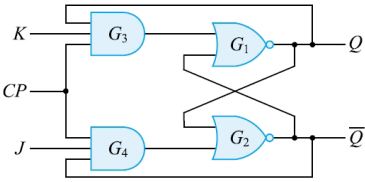

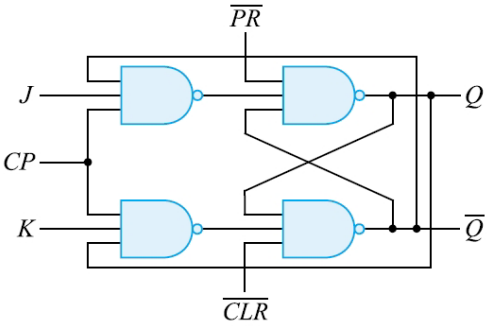

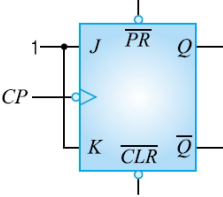

[참고] 비동기 JK 플립플롭의 회로도

| 회로도 | 논리기호 |

|---|---|

|  |

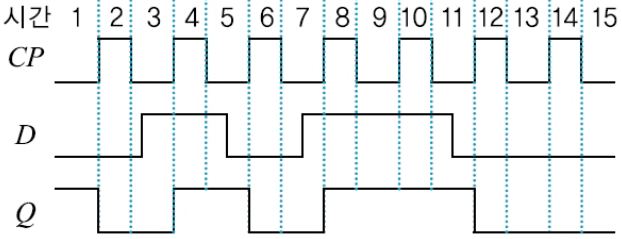

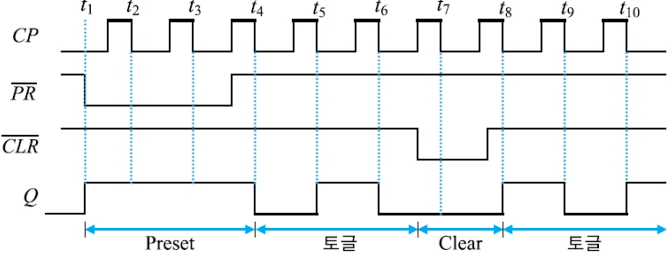

- 비동기 JK 플립플롭의 파형

|

2 Comments

네이스