2019년 1월 22일

CPLD (Complex Programmable Logic Device)

I. 복합 프로그래머블 논리 소자, CPLD

가. CPLD의 개념

- 내부에 논리 블록(PLD)과 이를 서로 연결해 주는 스위치 행렬이 내장된 반도체 소자

나. CPLD의 특징

| 중앙 스위치 방식 | – 양쪽 블록 사이에 스위치가 위치한 형태로 양쪽 블록을 배선 연결하여 로직 구성 |

| PAL 방식 구조 | – 일부 AND, OR gate가 고정되어 데이터에 따라 배선이 되는 구조 |

II. CPLD 구성도 및 구성요소

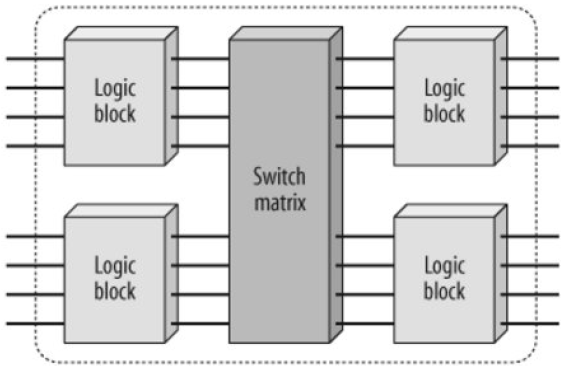

가. CPLD 구성도

|

- Logic block들이 중앙의 Switch Matrix를 이용하여 연결되는 구조

나. CPLD 구성요소

| 구성요소 | 설명 |

|---|---|

| Switch Matrix | – 각 Logic Block 사이에 중앙에 스위치가 연결되는 구조로 타이밍 예측이 용이 |

| Logic Block | – 복잡한 논리구조인 Macro cell에 대한 단선으로 논리회로 구성 |

| 소자 구성 | – EEPROM 또는 플래시 메모리로 소자 구성 |

다. 구현 방식

| 구현 방식 | 설명 |

|---|---|

| 프로그램 저장소 | – EEPROM이나 NAND 플래시에 반도체 설계 데이터 저장 후 기동 시 download |

| 프로그래밍 방법 | – 미리 내부에 구현되어 있는 빈 게이트들에 프로그래밍 정보를 입력 |

| 프로그래밍 특징 | – 비휘발성: 준비된 게이트들의 단선 통한 회로 구성으로 전원이 제거 되어도 유지 |

| 배선정보 디자인 | – 비휘발성 메모리 내 배선정보 저장 – Equation & Schematic |

III. 성능 명세 및 응용 분야/사례

가. 성능 명세

| 성능 명세 | 설명 |

|---|---|

| 성능 척도 | – Propagation Delay(지연시간) |

| 성능 | – 처리 속도 빠르며 속도 예측 가능 |

| 집적도 | – 수백 ~ 수천 게이트로 구성 |

| 소자크기 | – FPGA에 비해 작음 |

나. 응용 분야/사례

| 응용 분야 | 설명 |

|---|---|

| 응용 분야 | – 정밀한 타이밍으로 계측장비, 통신, 자동차 분야 등에 응용 |

| 응용 사례 | – 휴대폰, 차량용 네비게이션 등 |

- CPLD는 Macro Cell을 통과하는 delay가 일정하므로 micro-processor interface 활용 가능