2025년 11월 1일

CXL (Compute Express Link)

1. 초고속 인터페이스, CXL (Compute Express Link) 개요

| 개념 | CPU-디바이스 간 초고속 데이터전송 위해 PCIe에 구성되어 CXL.io/cache/mem 프로토콜 기반 링크를 제공하는 저지연 고속 인터커넥트 개방형 표준 기술 | |

|---|---|---|

| 특징 | 초 저지연 고속 링크 | – 데이터 전송 지연 감소 및 초고속 전송 |

| RDMA 성능 개선 | – 원격 호스트 내 메모리 직접 접근 개선 | |

| DRAM 용량 확장 | – CPU 당 최대 메모리 확장 지원 | |

| 이기종 장치 간 메모리 공유 | – 다양한 장치 간 메모리 공유 및 NoRAM 디바이스 지원 | |

- CXL은 PCIe 규격 기반으로 DDR RAM 등 주기억장치보다 속도는 느리나 CPU에 독립적이며, 높은 확장성을 통해 장치 간 HBM에 직접 접근하는 AI 데이터센터 등 메모리 중심 컴퓨팅에 필수 요소

2. CXL의 아키텍처 및 핵심 기술

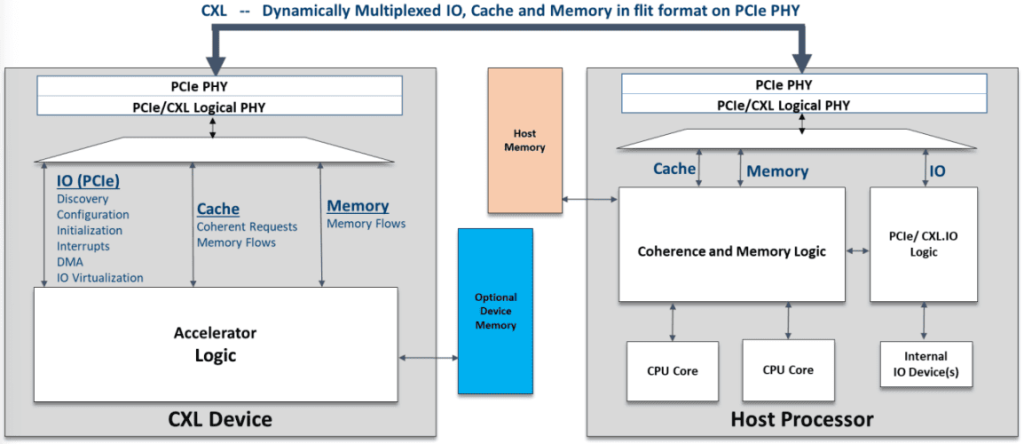

(1) CXL의 아키텍처

|

(2) CXL의 핵심 기술

| 구분 | 핵심 기술 | 역할 |

|---|---|---|

| 멀티프로토콜 기반 통신 | CXL.io | – 장치 제어 및 I/O 트랜잭션 처리 프로토콜 – PCIe와의 호환성 유지/제어, 관리 기능 담당 |

| CXL.cache | – CPU와 장치 간 캐시 일관성 지원 프로토콜 – 이기종 장치와 데이터 공유 시 무결성 확보 | |

| CXL.memory | – 확장 장치 메모리 직접 접근 지원 프로토콜 – Load / Store 통한 메모리 확장 및 공유 | |

| 메모리 및 생태계 확장 | Memory Pooling | – 다수 메모리를 하나의 Pool로 구성 – 다수 호스트, 장치 간 효율적 공유 |

| Memory Tiering | – 기존 DRAM 대비 느리지만 대용량의 메모리 지원을 통한 메모리 Tier2 확장 지원 | |

| PCIe 하위 호환 기술 | – 여러 CXL 장치 연결로 확장성 제공 – 기존 PCIe 기반 환경과 호환 |

- CXL은 초고속 데이터 전송을 위해 CXL.io, CXL.cache, CXL.memory 프로토콜을 사용하며, 여러 디바이스 타입(Type1, 2, 3)으로 용도별 활용

3. CXL 디바이스 타입 비교

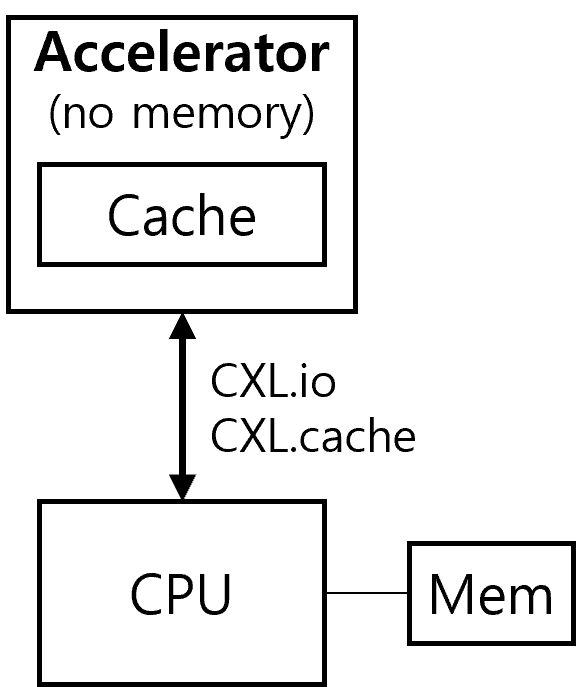

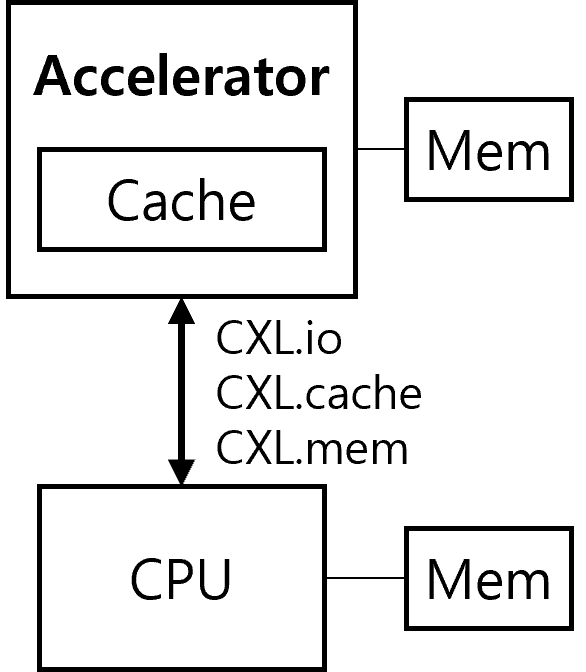

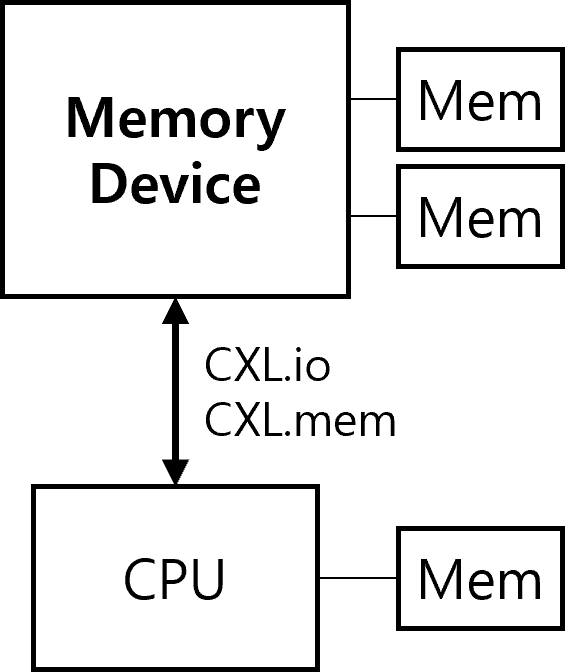

| 비교 항목 | Type1 Device | Type2 Device | Type3 Device |

|---|---|---|---|

| 구성도 |  |  |  |

| 용도 | – Caching Device/Accelerators | – Accelerator with Memory | – Memory Buffer |

| 특징 | – 자체 메모리 없는 스마트 NIC와 호스트 간 구성 | – 캐시와 호스트의 디바이스 메모리 일관성 보장 | – 메모리 버퍼나 SCM 연결 구성, 메모리 확장 |

| 사용 프로토콜 | – CXL.io – CXL.cache | – CXL.io – CXL.cache – CXL.memory | – CXL.io – CXL.memory |

| 활용형태 | – PGAS NIC, NIC atomics | – GPGPU, 고밀도 컴퓨팅 | – 메모리 성능/용량 확장 |

- CXL은 동일한 고속 인터커넥트 기술인 Nvidia NVLink와 경쟁중이며, 빅테크 기업들의 채용 여부에 따라 활성화 여부가 결정될 것으로 예상

[참고]

- CXL Consortium Blog, Introduction to Compute Express Link (CXL): The CPU-To-Device Interconnect Breakthrough, 2019.9

- 삼성전자 테크 블로그, 메모리 대역폭과 용량의 한계 확장: 삼성전자의 CXL 메모리 익스팬더, 2022.7