2018년 11월 21일

DMA (Direct Memory Access)

I. I/O로 인한 성능 감소 방지, DMA (Direct Memory Access)

(1) DMA(Direct Memory Access) 개념

- I/O로 인한 성능 감소 방지 위해 CPU 개입 없이 I/O 장치와 기억장치 간 직접 데이터 전송 방식

(2) DMA I/O와 Direct I/O 환경 비교

| DMA I/O | Direct I/O(DMA 미사용) |

|---|---|

| – DMA 기반 Data 처리 중 CPU는 다른 프로세스 처리 | – Data I/O 처리 시 완료까지 작업 중지, CPU 대기 필요 |

II. DMA 구성도/구성요소 및 동작모드

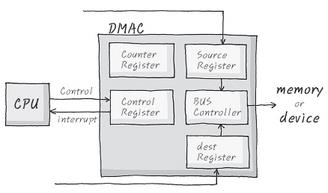

(1) DMA 구성도/구성요소

| 구성도 | 구성요소 | 설명 |

|---|---|---|

| 주소 레지스터 | – I/O 장치 주소 |

| 데이터 레지스터 | – 데이터 버퍼 | |

| 계수 레지스터 | – 전송 Data 수 | |

| 컨트롤 레지스터 | – 전송 모드 | |

| 제어 회로 | – 신호 발생 회로 |

- DMA 기반 전송 위한 중앙처리장치 버스 신호와 레지스터로 구성

DMA 동작 모드

| 구분 | 개념도 | 설명 |

|---|---|---|

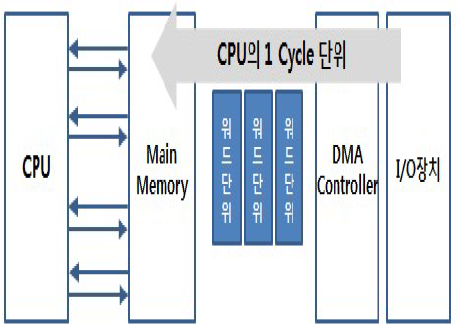

| Cycle Stealing (Word) |  | – Word 단위 데이터 전송 – DMAC와 CPU 동시 BUS 요청 시 DMA 우선권 |

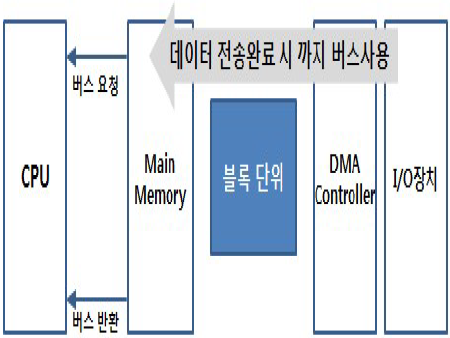

| Burst Transfer (Block) |  | – Block 단위 데이터 전송 – 여러 메모리 워드로 구성 – Block 전송 시 BUS독점 |

- CPU가 시스템 미사용 시 DMA가 BUS 사용하는 Interleave DMA 모드도 존재

III. DMA 동작 순서 및 주요 구성요소

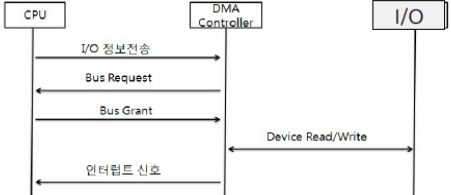

(1) DMA 동작 순서

| DMA Controller | DMA 동작 순서 |

|---|---|

|

(2) DMA 주요 구성요소

| 구분 | 구성요소 | 설명 |

|---|---|---|

| 명령어 | – DMA Select(DS) – Register Select(RS) | – 주소 버스로 DS, RS enable하여 DMA Register 선택 |

| – BUS Request(BR) | – DMAC를 통해 버스 요청 – add/data 버스 제어권 양도 | |

| – BUS Grant(BG) | – BR에 따른 상태 변경 후 DMA BUS 사용 가능 알림 | |

| 레지 스터 | – Address Register | – 메모리의 접근 주소 저장 – Work 전송 후 Increment |

| – Word Count Register | – 전송할 블록 Word 수 저장 – Work 전송 후 Decrement | |

| – Control Register | – 레지스터 동작 모드 설정 – Burst Mode, Cycle Stealing |

- DMA는 하나의 Instruction에 하나의 Block I/O를 처리하는 방식으로 하나의 Instruction에 여러 Block I/O를 처리하는 채널제어 방식과 차이

IV. DMA와 채널제어 방식 비교

| 항목 | DMA | 채널제어 |

|---|---|---|

| 처리 단위 | – 하나의 Instruction에 하나의 Block I/O | – 하나의 Instruction에 여러 Block I/O 처리 |

| 메모리 | – 기억장치 필요 | – 로컬 메모리 기반 데이터 블록 저장 |

| 활용 | – 소형 컴퓨터 – PC, 태블릿 등 | – 대형 컴퓨터 – 대용량 서버 |

- DMA와 채널제어 방식은 모두 중앙처리장치(CPU) 개입없이 I/O를 수행하며, DMA는 PC, 채널 제어방식은 대형 서버에서 주요 사용