2019년 1월 23일

FPGA (Field Programmable Gate Array)

I. 논리 소자 간 배선 연결, FPGA

가. FPGA의 개념

- 논리소자 간 배선을 프로그래밍하여 다양한 로직 구성을 가능하게 하는 반도체 소자

나. FPGA의 특징

| SRAM 방식 | – 모든 로직 블록에 배선을 연결할 수 있어 다양한 구조의 회로 구성 가능 |

| 휘발성 배선 정보 | – 배선 정보가 외부에 있는 플래시 메모리에 저장되어 있어 기동 시 SRAM에 다운로드 |

II. FPGA 구성도 및 구성요소

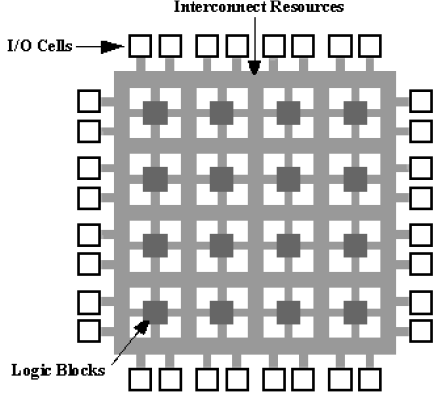

가. FPGA 구성도

|

- 내부에 Logic Block이 있고 이를 연결하기 위해 배선이 존재

나. FPGA 구성요소

| 구성요소 | 설명 |

|---|---|

| Logic Block | – CLB 기반으로 4-input LUT(Lookup Table)와 D플립플롭으로 구성 |

| I/O cell | – Chip의 I/O 신호를 받아오고 다시 보낼 때 I/O cell 사용 |

| Interconnect Resources | – 프로그래밍이 가능하여 Logic Block 연결 시 지연 방지 |

다. 구현 방식

| 구현 방식 | 설명 |

|---|---|

| 프로그램 저장소 | – 플래시 메모리를 외부에 두고 내부에는 휘발성 SRAM을 고밀도로 나열 |

| 프로그래밍 방법 | – CLB 기반 구조적 연결 – 모듈을 조합하여 의도하는 기능 구현 |

| 프로그래밍 특징 | – 휘발성: 전원이 제거되면 회로구성이 초기화 |

| 배선정보 디자인 | – 기동 시 배선정보 다운로드 필요 – Schematic & HDL |

III. 성능 명세 및 응용 분야/사례

가. 성능 명세

| 성능 명세 | 설명 |

|---|---|

| 성능 척도 | – Maximum Clocking Frequency (Fmax) |

| 성능 | – 상대적 느리며 응답시간 예측 어려움 |

| 집적도 | – 수백만 게이트로 구성 |

| 소자크기 | – CPLD에 비다 소자 크기 큼 |

나. 응용 분야/사례

| 응용 분야 | 설명 |

|---|---|

| 응용 분야 | – 디지털 신호 처리 프로세서 (DSP) – 주문형 반도체(ASIC) 프로토타입 |

| 응용 사례 | – 의료 영상 알고리즘 구현 – 하이브리드 TV 수신기 개발 |

- FPGA는 Control Block이나 Random Logic, 플립플롭을 많이 사용하는 디자인 활용 필요

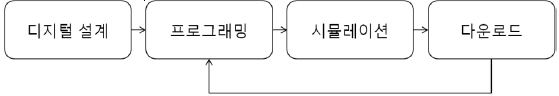

IV. FPGA 디지털 설계 과정

| 구분 | 절차 | 설명 | |

|---|---|---|---|

| 전체과정 |  | ||

| 디지털 설계 | 논리식 | – PALASM, ABEL 등 논리식 전용 표현 언어 사용 | |

| HDL | – VHDL, Verilog, ABEL-HDL 등 사용 – 다양한 상용 Tools에서 HDL 지원 | ||

| 회로도 | – FPGA/CPLD Vendor에서 제공하는 회로도 작성 tool 이용 | ||

| 파형 입력 | – 타이밍도 이용, 회로동작을 신호의 ON/OFF로 표현 설계 | ||

| State machine | – FPGA/CPLD Vendor에서 제공하는 State machine editor 사용 | ||

| 프로그래밍 | Define I/O | – 신호 별 세부기능에 관한 기술문서 작성 | |

| Design Entry | – HDL(VHDL/Verilog HDL) Design Files – Schematic Diagram | ||

| Logic Synthesis | – Library, Design Files 조합 netlist 작성 (netlist: 실제 H/W 구성위한 gate 명세) | ||

| 시뮬레이션 | Function Simulation | – Test Vector, Test Brench 파일 등 이용하여 회로 기능 검사 | |

| Map, Place, Route | – 중간 출력 파일, User constraints file | ||

| Timing Simulation | – Test Vector에 관련 기술문서, Timing Simulation 분석 결과 | ||

| 다운로드 | 써넣기 데이터 만들기 | – 범용 라이터기 사용 ‘써넣기’ 시 표준형인 JEDEC 포맷 데이터로 써넣음 – SRAM 구조는 전용 포맷으로 작성 – JEDEC 포맷의 써넣기 데이터 및 SRAM으로 다운로드 포맷은 각 Vendor 제공 tool에 포함 | |

- 디지털 설계 시 최종 배포 직전까지 Debug 가능하므로 생산성 향상

V. FPGA 디지털 설계원리

| 설계 원리 | 설명 |

|---|---|

| 동기화된 FPGA 설계 습관 | – 좋은 설계 습관은 설계 목표 충족 – Propagation Delay 의존성과 불완전 타이밍 분석, 일시적 오류 해결 |

| 클록 시그널 베이스 설계 | – 클록 시그널이 모든 이벤트를 트리거 – Rising Edge에 모든 Register 정보 갱신 |

| Combinational Login 구조회피 | – Combinational Loop로 발생 인한 불안정성과 신뢰성 저하를 최소화 – 모든 백루프는 레지스터 포함 필요 |

| Delay Chain 회피 | – 2개 이상의 연속 노드가 딜레이를 유발하도록 사용되는 경우 Delay Chain 발생 |

| Latch 회피 | – Latch 타이밍이 모호한 편이므로 glitch(일시적 시스템 장애) 발생 가능 – Latch는 레지스터에 비해 낮은 성능 – FPGA는 매우 많은 량의 레지스터 보유 |

| 리셋 지원 | – 디바이스에서 비동기식 리셋핀 활용, 전체 리셋 기능 지원 |

| 벤더 특성 반영 | – 벤더 제공 특수 기능 확인 필요 – 해당 기능 적절히 활용이 중요 |