2019년 1월 18일

PLD (Programmable Logic Device)

I. 회로 구조 변경 가능, PLD

가. PLD(Programmable Logic Device)의 개념

|

- ASIC과 달리 제조 후 사용자가 내부 논리회로의 구조를 변경할 수 있는 집적회로

나. PLD의 장점

| Total Cost 절감 | – 컨트롤블록 조립, 수리/개발 비용 절감 |

| Time To Market | – 생산 시간 획기적 단축, 시장대응 확보 |

| Risk 감소 | – 생산 완료 직전까지 수정 가능 |

| 부품 절감 | – 컴포넌트 및 PCB 사이즈 축소 가능 |

II. PLD 유형과 성능 명세 비교

| 유형 | 설명 |

|---|---|

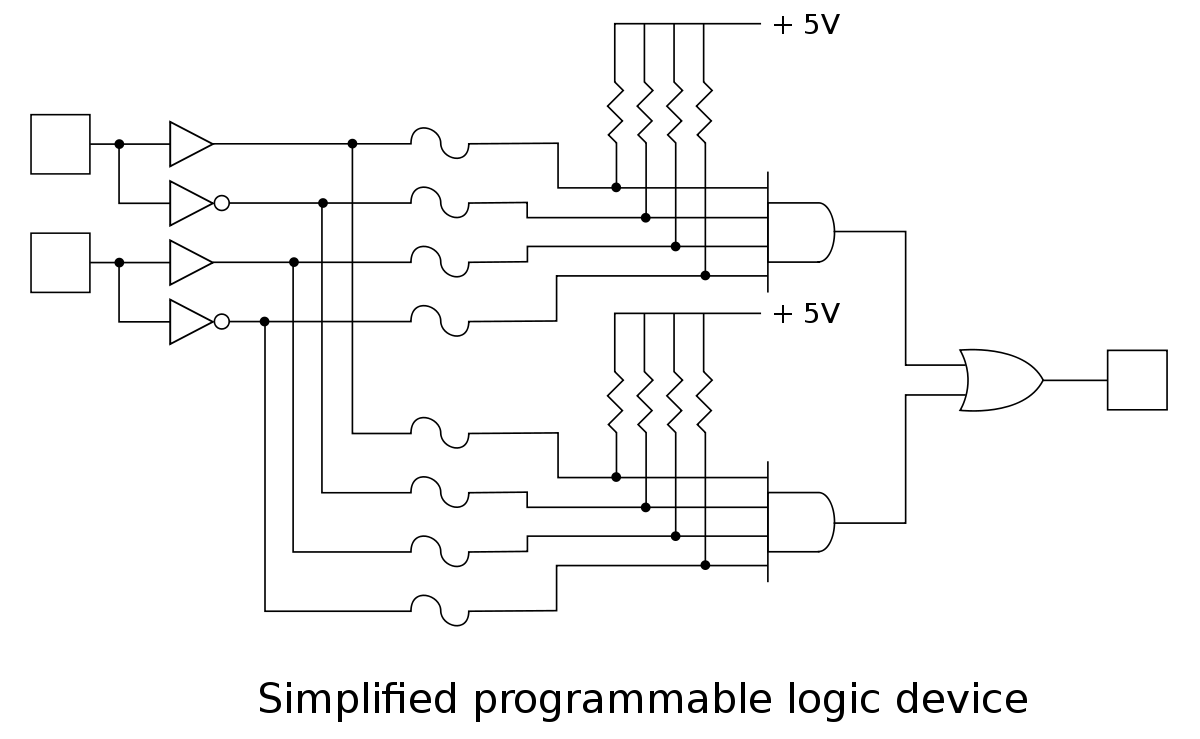

| PLA | – Programmable Logic Array – AND, OR Plane 연결 재설정 가능 – 다양한 사이즈로 구현 가능 |

| PAL | – Programmable Array Logic – AND Plane만 재설정 가능, OR Plane은 고정 – PLA보다 저렴하며 빠르고 간단하게 생산 가능 |

| CPLD | – Complex Programmable Logic Device – 2 ~ 100개의 PAL Block 사용 – XOR, MUX, tri-state gates 지원 |

| FPGA | – Field Programmable Gate Array – AND/OR Plane 사용하지 않음 – 로직 및 I/O 블록, 스위치, 내부연결 지원 – Configurable Logic Block(CLB), Switch Matrix |

나. 각 유형 별 세부 명세 비교

| 항목 | PLA/PAL | CPLD | FPGA |

|---|---|---|---|

| Cost | USD 2 ~ 15 | USD 5 ~ 50 | USD 10 ~ 300 |

| Macro-cell | 8 ~ 10 | 32 ~ 128 | 100 ~ 1000 |

| Pins | 20 ~ 24 | 44 ~ 160 | 84 ~256 |

| Prop. Delay | 5 | >8 | 5~10 per CLB |

| Clocks | 1 | 2 ~ 4 | >2 |

| device | AMD22V10 | Cypress 7C372 | Xilinx 4033 |

| Configuration | EEPROM | EEPROM | RAM or OTP |

| Design | Boolean equations | HDL or schematic | HDL or schematic |

- 세부 성능과 목표 시스템의 요구사항을 비교하여 가장 적합한 PLD 선정하여 최적화 제품 선택하는 것이 중요