2018년 12월 20일

TLB (Translation Look-aside Buffer)

1. 가상메모리 페이징 속도향상, TLB (Translation Look-aside Buffer)

(1) TLB (Translation Look-aside Buffer)의 정의

- 자주 참조되는 가상 메모리 주소를 실제 메모리 주소로 매핑 시 성능 개선 위해 MMU에서 사용하는 고속 캐시

(2) TLB의 특징

| 특징 | 설명 |

|---|---|

| 변환 결과 테이블 | – 매번 주소를 변환하는 대신 변환 결과를 테이블에 저장하여 사용 |

| 특수 고속 캐시 | – 페이지 테이블 항목에 대한 특수 고속 캐시 사용하여 메모리 참조 시간 단축 |

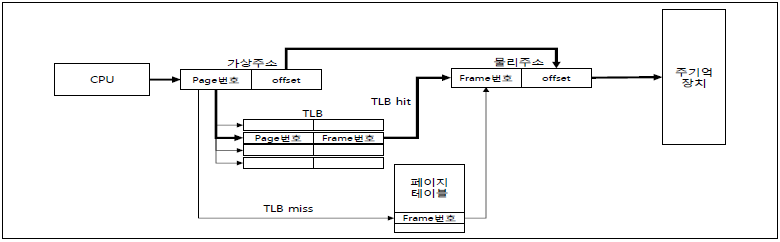

2. TLB의 개념도 및 동작원리

(1) TLB의 개념도

(2) TLB의 동작원리

| 방안 | 상태 | TLB 동작 |

|---|---|---|

| TLB Hit | – 가상 주소에 해당 항목이 TLB에 있음 | – CPU가 TLB 통해 즉시 물리주소 생성 |

| TLB Miss | – 가상 주소에 해당 항목이 TLB에 없음 | – 주기억장치 페이지테이블 참조, TLB 갱신 |

| 페이지 Fault | – 가상 주소에 해당 항목이 주기억장치에 없음 | – 디스크에서 페이지 반입, 페이지테이블 갱신 |

(3) 직접사상 방식과 TLB의 비교

| 항목 | 직접 사상의 주소 변환 | TLB에 의한 주소 변환 |

|---|---|---|

| 사상 방식 | – Direct Mapping | – Association Mapping |

| 페이지 테이블 위치 | – 주기억장치 내 | – 고속의 특수 캐시 내 (TLB) |

| 장단점 | – 데이터 접근시 주기억장치 두 번 접근 필요 | – TLB 병렬 고속탐색 – 고비용, 적용 한계 |

3. TLB 성능 개선 위한 고려사항

| 고려사항 | 상세 내용 |

|---|---|

| Entry 수 증가 | – TLB 참조 증가, 많은 전력 사용 |

| 페이지 크기 증대 | – 사상 적용 증가, 내부 단편화 증가 |

| 다중 페이지 지원 | – 적은 내부 단편화, 큰 페이지 사용 가능 |

3 Comments

TLB_MISS -> PAGE_TABLE_MISS -> DISK로 가서 다시 PAGE_TABLE로 가서 다시 TLB로 가는건가요?? 아니면 DISK에서 곧 바로 TLB로 가는건가요?

결론적으로 말씀드리면 Page Fault 시 Disk -> Page Table update -> TLB update 순서로 수행됩니다.

좀더 자세하게 설명드리면, TLB miss 및 Page Fault 발생 시 Disk에서 필요 Data를 Access해서 메모리에 적재해야 하는데 이 작업이 오래 걸리기 때문에 OS에서는 아래 순서대로 수행됩니다.

① CPU에서 현재 수행중인 프로세스를 Wait State로 변경시키고 Disk I/O 프로세스로 Context Switching 합니다.

② Disk에 있는 Data를 메모리에 적재하는 동작이 끝나면 Interrupt가 발생하고, OS는 Page Table을 update 후 Wait Queue에 있는 수행 프로세스를 Ready Queue로 옮깁니다.

③ Ready Queue에 있는 프로세스는 스케줄링에 의해 차례가 되면 다시 CPU를 할당 받습니다.

④ 현재 Page Table만 update 되어 있으므로, 프로세스가 재실행되면 TLB miss가 다시 발생하고 이후 과정은 TLB miss일 때와 동일하게 동작합니다.

오 깔끔한 정리 감사합니다. ^^