2024년 5월 2일

다단계 페이지 테이블(Multi-level Page Tables)

1. 고정 크기 분산 메모리 할당, 페이징 기법의 개요

(1) 페이징 기법의 개념

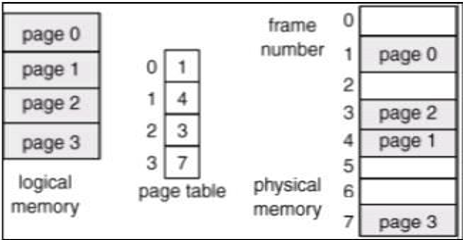

| 개념 | 개념도 |

|---|---|

| 메모리를 고정 크기의 프레임으로 나누어 페이지 번호와 프레임 번호를 맵핑하여 분산 할당하는 메모리 관리 기법 |  |

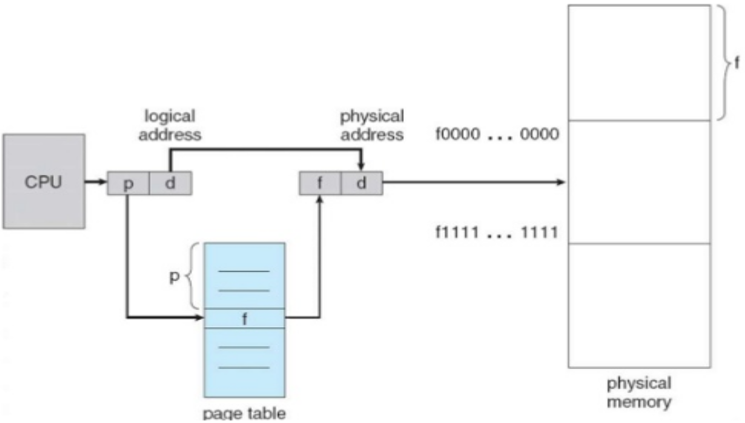

(2) 페이징 기법의 메커니즘

p: page number, f: frame No. (physical address), d: page offset | |

| ① | logical address의 주소 이용 page number 확보 |

| ② | page table에서 해당 page에 있는 frame number 확보 |

| ③ | frame number + page offset으로 물리 메모리 주소 확인 |

- 32bit 환경(offset(12bit), page number(20bit))에서 212(4KB) 페이지 엔트리가 220개로 구성, 페이지 테이블 항목은 4 byte이므로 프로세스 별 4MB (=4 byte x 220) 페이지 테이블 필요

- 다수 프로세스의 페이지 테이블 사용에 따른 메모리 자원 관리의 비효율성 해결 위해 페이지 번호를 나누어 필요한 부분만 메모리에 적재하는 다단계 페이지 테이블 필요

- 프로세스 증가로 인한 페이지 테이블 엔트리 추가 시 4KB 페이지 테이블을 추가하여 맵핑

2. 다단계 페이지 테이블 (Multi-level Page Tables)

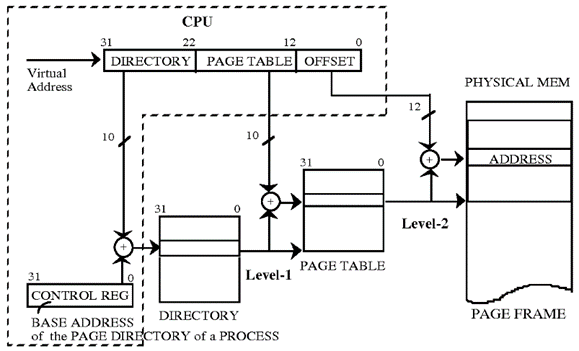

(1) 다단계 페이지 테이블 기반 주소 변환 구성도

|

(2) 다단계 페이지 테이블 기반 주소 변환 상세 절차

| # | 상세 절차 |

|---|---|

| ① | 페이지 테이블 시작 주소(Base Address)와 논리 주소 내 1차 페이지 테이블(디렉토리) 주소 기반 1차 페이지 테이블(디렉토리)에 존재하는 2차 페이지 테이블 시작 주소 확인 |

| ② | ① 단계에서 확인된 2차 페이지 테이블 시작 주소와 논리 주소 내 2차 페이지 테이블 주소 기반 메인 메모리의 기준 주소 확인 |

| ③ | 메인 메모리 기준 주소와 12bit 변위(Offset)를 통해 접근해야할 메모리 주소 확인 |

- 다단계 페이지 테이블은 페이징의 메모리 관리 비효율성을 해결할 수 있으나, 단계가 많아질수록 복잡도가 증가하며, 프로세스 증가에 따른 페이지 테이블 크기 증가 문제점의 근본적 해결은 불가

- 프로세스가 아닌 메모리 프레임 기준으로 맵핑하는 역페이지 테이블(Inverted Page Table)로 크기 증가 문제를 해결

[참고]

- 홍릉과학출판사, Operating System Concepts 8th Edition

- 한빛아카데미, 컴퓨터 구조와 원리 2.0