2020년 1월 29일

중앙 처리 장치(CPU)의 Major State

I. 중앙 처리 장치(CPU)의 Major State의 개요

가. Major State의 개념

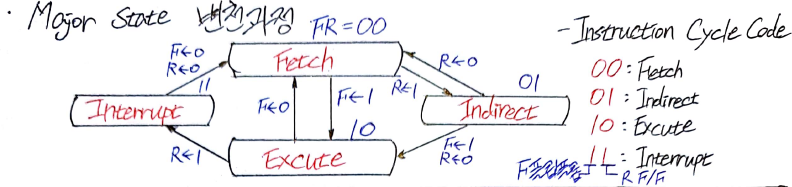

- Fetch, Indirect, Execute, Interrupt의 4가지 형태로 CPU가 현재 수행하는 작업의 상태

나. Major State의 특징

- 4가지 단계를 반복적으로 거치며 동작을 수행하고 플립플롭을 통해 상태 변천

- 메이저 상태 레지스터를 통해 현재 상태 확인 가능

II. Major State의 변천과정과 동작

가. Major State 변천과정

|

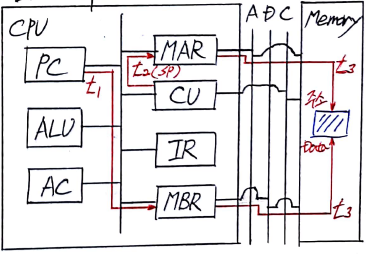

나. Major State 별 Data 흐름도와 동작 과정

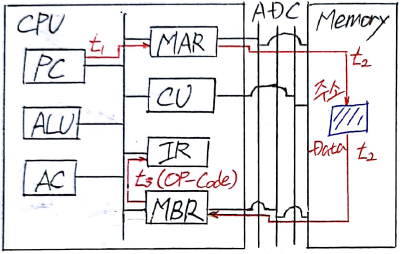

- Fetch State

| 흐름도 |  |

| 설명 | 주기억장치에서 중앙처리장치의 명령 레지스터로 명령어를 가져와 해독하는 단계 |

| 동작 과정 | [t1 단계] MAR ← PC : PC(Program Counter)의 번지를 MAR에 전송 [t2 단계] MBR ← M[MAR] : MAR 지정 메모리 내용( 주기억장치의 명령 )을 MBR에 저장 PC ← PC + 1 : 부 프로그램 시작 [t3 단계] IR ← MBR[OP] : OP-Code 에 해당하는 명령을 명령 레지스터에 전송 I ← MBR[I] : 모드 비트를 플립플롭에 전송 – 모드 비트(I)가 0 이면, F 플립플롭에 1 전송하여 Execute State로 변천 |

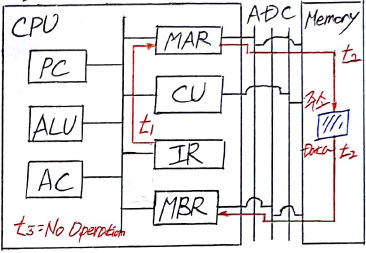

- Indirect State

| 흐름도 |  |

| 설명 | 인출 단계에서 해석된 명령어의 주소부가 간접주소인 경우 수행되는 단계 |

| 동작 과정 | [t1 단계] MAR ← IR(ADD) : IR(명령어의 주소)의 내용을 MAR에 전달 [t2 단계] MBR ← M[MAR] : MAR이 지정하는 메모리의 내용을 MBR에 저장 [t3 단계] No Operation – F 플립플롭에 1을, R 플립플롭에 0을 전송하여 Execute State로 변천 |

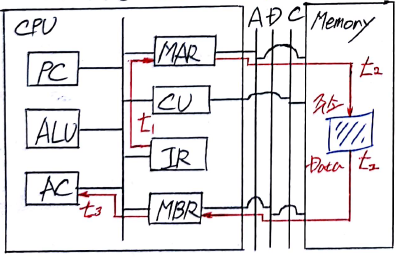

- Execute State

| 흐름도 |  |

| 설명 | 해독된 명령을 실행하는 단계 |

| 동작 과정 | [t1 단계] MAR ← IR(ADD) : IR(명령어의 주소)의 내용을 MAR에 전달 [t2 단계] MBR ← M[MAR] : MAR이 지정하는 메모리의 내용을 MBR에 저장 [t3 단계] AC ← AC + MBR : MBR의 내용을 누산기에서 계산 – F 플립플롭에 0을 전송하여 Fetch State로 변천 – R 플립플롭에 1을 전송하여 Interrupt State로 변천 |

- Interrupt State

| 흐름도 |  |

| 설명 | 인터럽트 발생 시 서브루틴(부프로그램)의 호출 단계 |

| 동작 과정 | [t1 단계] MBR ← PC : MBR에 PC값(Program Counter, 다음 실행할 명령의 주소) 저장 [t2 단계] MAR ← SP : MAR에 현재 SP값(Stack Pointer, 복귀 주소) 저장 PC ← ISR 시작 주소 : PC(Program Counter)에 ISR(인터럽트 서비스 루틴) 시작 주소 지정 [t3 단계] M[MAR] ← MBR : 복귀 주소(t2 단계 SP값)를 저장한 주소에 MBR의 데이터(t1단계 PC값) 저장 – 인터럽트 종료 후 F, R 플립플롭에 0을 전송하여 Fetch State로 변천 |

- 인터럽트 발생 시 인터럽트 벡터 테이블(IVT) 조회 후 인터럽트 ID에 해당하는 처리 루틴으로 분기