2023년 8월 26일

HBM (High Bandwidth Memory)

1. DRAM 적층형 고성능 메모리, HBM의 개요

(1) HBM의 부각 배경

- 인공지능, 자율주행, 스마트 서비스 등 신기술 확산으로 대량 데이터 처리용 고성능 연산 수요 촉발

- ChatGPT 등 초거대 인공지능 경쟁의 본격화로 고용량 데이터 처리에 최적화된 메모리 반도체 필요

- 폰노이만 컴퓨팅 구조의 데이터 이동 병목 현상 한계 해소, 저전력, 고속 연산 가능한 HBM 부각

(2) HBM(High Bandwidth Memory)의 개념

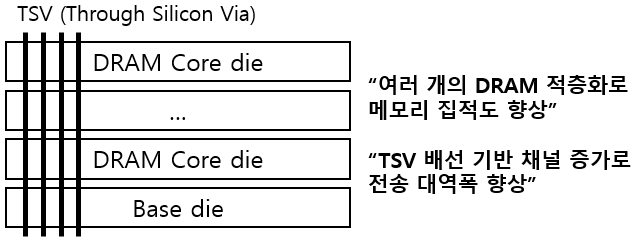

| 개념도 |  |

|---|---|

| 개념 | 고성능 데이터 처리를 위해 DRAM 적층화 및 TSV 배선 기반 데이터 이동 병목 현상을 해소한 DRAM 적층형 고성능 메모리 |

- HBM은 TSV(Through Silicon Via) 배선을 통해 1,000개 이상의 핀을 탑재하여 데이터 이동 병목 현상을 해소하고 인공지능 연산 등 고성능 데이터 처리에 적합

2. HBM의 아키텍처 및 구성요소

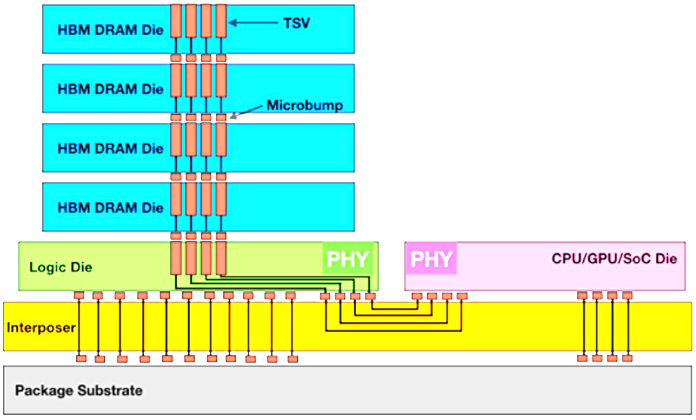

(1) HBM의 아키텍처

|

(2) HBM의 구성요소

| 구분 | 구성요소 | 역할 |

|---|---|---|

| 메모리 적층화 | TSV | DRAM Die를 뚫어 전도성 재료를 채운 수직 실리콘 관통 전극 |

| DRAM die | DRAM Cell 그룹, 패키징 단위 | |

| Base(Logic) die | 다른 칩셋 및 PHY와 DRAM die 연결 | |

| Micro Bump | 미세 돌기모양 금속으로 반도체 간 접합 연결 | |

| 칩셋 구성 | SoC | System on Chip, 그래픽 및 명령어 처리 프로세서 |

| PHY | Base die와 Process die 간 연결하는 물리 계층 인터페이스 | |

| Silicon Interposer | 다수 범프 수용 위해 패드/금속 배선으로 HBM, Logic Chip 연결 | |

| Package Substrate | HBM, SoC, CPU, GPU 칩 등을 연결하는 PCB 기판 |

- HBM은 저전력, 고대역폭, 메모리 집적도가 높지만 공정 난이도가 높으며 낮은 수율, DRAM 대비 제조 비용이 높아 인공지능 데이터 처리 등 특정 분야에서 사용

- 아직 전체 DRAM 시장에서 차지하는 비중은 작으나 대용량 데이터의 고속 처리 연산 수요가 폭발적으로 늘어날 것으로 예상되므로 성장 가능성이 높음

3. HBM의 DDR 기반 메모리 대비 장단점 및 스펙 비교

(1) HBM의 DDR 기반 메모리 대비 장단점

| 장점 | 단점 |

|---|---|

| – 높은 대역폭으로 데이터 이동 병목 현상 해소 – DRAM 수직 집적화로 공간 효율성 향상 – DDR 메모리 대비 전력 효율성 우위 | – 높은 공정 난이도 – 낮은 수율 – DDR 기반 메모리 대비 높은 제조 비용 |

(2) HBM와 DDR 기반 메모리 스펙 비교

| 비교 항목 | HBM3 | GDDR6 |

|---|---|---|

| 용도 | AI 학습용 | 그래픽 카드, AI 추론용 |

| Pin Data Rate | 6.4 Gbps | 16 Gbps |

| Pin | 1,024개 | 32개 |

| Bandwidth | 819 GB/s | 64 GB/s |

- HBM은 DDR 기반 메모리에 비해 핀 당 속도는 낮지만 TSV 배선을 통해 다수 핀을 배치하여 고속 데이터 이동을 통해 인공지능 데이터 처리 연산에 적합

- 인공지능 산업이 본격적으로 확대되고 있어 SK하이닉스, 삼성전자, 마이크론 등 HBM 제조사들이 고성능 메모리 제품 개발 및 설비투자를 확대하고 있으며, 엔비디아, AMD, 인텔 등 GPU 기업이 HBM의 최대 수요처로 부상

- 최근 범프를 이용한 DRAM 적층 기술의 한계로 인해 반도체 칩 사이를 구리(copper)로 직접 연결하는 하이브리드 본딩 적용 연구/개발 중이며, DRAM 적층 20단 HBM4E 부터 상용화 예상

[참고]

- KB 지식 비타민, 인공지능 시대 새로운 성장 동력 HBM(고대역폭메모리), 2023.7

- SK하이닉스, HBM3 혁신을 선도한다, 2022.6