2026년 5월 2일

NPU (Neural Processing Unit)

1. AI 모델 연산 최적화 프로세서, NPU의 개념 및 특징

(1) NPU (Neural Processing Unit)의 개념

| 개념 | AI 데이터 고속 처리 위해 MAC 배열, 양자화 기반 딥러닝 연산에 최적화된 신경망 처리 장치 | |

|---|---|---|

| 특징 | 문제 분해 및 병렬 처리 | – 문제를 구성 요소로 분해하여 멀티태스킹 문제 해결하고 여러 신경망 연산을 동시 실행 |

| 저정밀도 기반 에너지 효율화 | – AI 모델 학습 시 고정밀도(FP32 등) 사용하지만 추론 시 저정밀도(INT8 등)로 변환하여 계산 복잡성 감소, 에너지 효율 극대화 | |

| 고대역폭 메모리 | – 대규모 데이터가 필요한 AI 처리 작업을 효율적으로 수행하기 위해 칩 내부에 고대역폭 메모리 탑재 | |

| AI 연산 최적화 하드웨어 가속 | – 신경망 Layer간 중간 데이터를 칩 내 직접 처리, ‘0’ 포함 행렬 연산 생략 등 하드웨어 차원의 AI 데이터 연산 가속 | |

2. NPU의 아키텍처 및 기술 요소

(1) NPU의 아키텍처

|

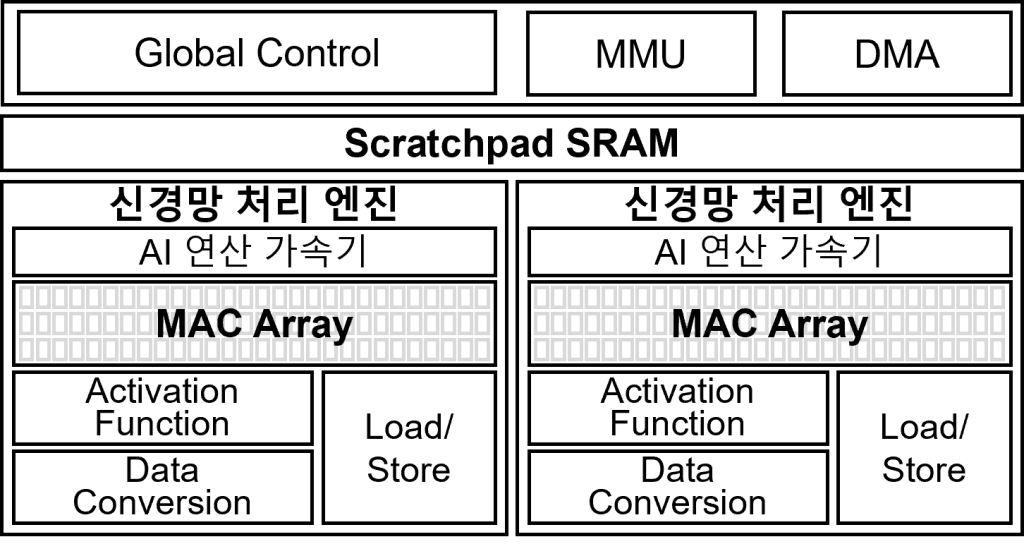

- 신경망 Layer 중간 데이터 저장을 위한 대용량 고속 Scratchpad 메모리와 행렬 곱셈 등 AI 연산 위한 신경망 처리 엔진으로 구성

(2) NPU의 핵심 기술 요소

- MAC(Multiply-Accumulate): ‘곱셈-누산’ 연산기

| 구분 | 기술 요소 | 역할 |

|---|---|---|

| 핵심 연산 아키텍처 | MAC 연산기 배열 (MAC Array) | – 입력값과 가중치 연산 과정을 1클럭 사이클에 처리 – 다수 MAC 유닛을 배열 집적하여 대규모 병렬 연산 |

| 데이터 플로우 아키텍처 (Dataflow Architecture) | – 데이터가 연산기 배열을 따라 규칙적 전달 – 가중치, 출력값 등 레지스터에 고정하여 재사용 | |

| 데이터 및 연산 경량화 | 양자화 및 저정밀도 연산 (Quantization & Low-Precision) | – 데이터를 8/16비트(INT8, FP16 등) 변환 연산 – 데이터 크기 감소로 대역폭 한계 극복, 성능 극대화 |

| 희소성 가속 기술 (Sparsity Acceleration) | – ‘0’ 포함 행렬 연산을 미리 감지하고 연산 생략 – 유의미한 데이터만 사용, 불필요 연산 낭비 제거 | |

| 자원 관리 및 시스템 오케스트 -레이션 | 온칩 메모리 계층 구조 (On-chip Mem. Hierarchy) | – 칩 내부에 대용량 고속의 Scratchpad SRAM 탑재 – 신경망 Layer간 중간 데이터를 칩내 직접 처리 |

| 소프트웨어 스택 및 컴파일러 (S/W Stack & Compiler) | – AI 모델 분석하여 노드 통합, 메모리 최적화 – 데이터를 효율적 순서/크기로 NPU에 분할 할당 |

- NPU는 인공지능의 핵심인 딥러닝 알고리즘을 효율적으로 처리하기 위해 설계된 전용 하드웨어이며, CPU나 GPU와 달리 행렬 연산과 병렬 처리에 최적화되어 있어 높은 전력 효율과 고속 AI 데이터 연산 가능

3. CPU, GPU, NPU 비교

| 비교 항목 | CPU | GPU | NPU |

|---|---|---|---|

| 아키텍처 구조 | 소수 Fat Core, 파이프라인 | 수천개의 Thin Core, SIMT | 2D/3D MAC Array (Systolic Array) |

| 병렬성 | ILP (명령어 수준 병렬성) | TLP (스레드 수준 병렬성) | Data-Level (행렬 단위 병렬화) |

| 최적화 목표 | 지연 시간 최소화 | 처리량 극대화 | 전력 대비 성능, 행렬 연산 성능 극대화 |

| 제어 로직 | 파이프라인 분기 예측 | 하드웨어 멀티스레딩 | 소프트웨어 스케줄링 |

| 메모리 계층 | Multi-level Cache | HBM + 공유 메모리 | Massive On-chip 메모리 |

| 주요 연산 단위 | Scalar (ALU) | Vector (ALU Array) | Tensor (MAC Array) |

| 데이터 정밀도 | FP64, FP32, INT64 | FP32, FP16 | INT4/8, FP16, BF16 |

| 프레임워크 | C/C++, JAVA 등 | CUDA, OpenCL 등 | PyTorch 등 |

- CPU와 GPU는 개발자가 직접 메모리와 스레드를 통제(Low-level control)해야 성능을 끌어올릴 수 있는 반면, NPU는 칩 아키텍처가 특정 프레임워크 연산(그래프)에 고정되어 있으므로, 개발자가 칩을 직접 제어하기보다는 AI 컴파일러가 코드를 하드웨어 언어로 번역하고 쪼개는 역할이 절대적으로 중요

[참고]

– Google, Noman Jouppi 외, In-Datacenter Performance Analysis of a Tensor Processing Unit, 2017

– IBM, Josh Schneider 외, What is a neural processing unit (NPU)?

– Intel, Quick overview of Intel’s Neural Processing Unit (NPU)