2024년 6월 18일

PIM (Processing-in-Memory)

1. PIM (Processing-in-Memory)의 개요

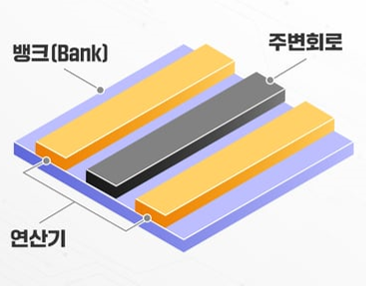

(1) PIM의 개념 및 필요성

| 개념 | 필요성 |

|---|---|

| CPU-메모리 병목으로 인한 작업 처리 성능 저하 극복 위해 메모리 칩 내 연산기를 배치하여 데이터 이동 최소화 기반 작업 처리 성능을 향상시키는 메모리 반도체 | – 폰노이만 아키텍처 한계 극복 – 인공지능, 빅데이터 실시간 처리 – 데이터 병목 현상 최소화 – 메모리 내 연산으로 성능 향상 |

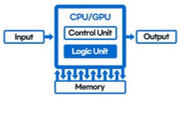

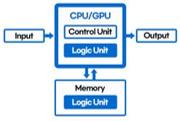

(2) 기존 아키텍처(폰노이만 구조)의 한계점과 PIM 구조 통한 극복

| 폰노이만 구조의 한계점 | PIM 구조를 통한 극복 |

|---|---|

|  |

| CPU-메모리 간 대량의 데이터 이동이 필요하므로 작업 처리 지연 및 성능 저하 한계점 발생 | CPU-메모리 간 데이터 이동 최소화를 통해 작업 처리 지연 및 성능 저하를 극복 |

- PIM 기술은 CPU와 메모리가 분리되어 있는 폰노이만 구조의 한계점인 메모리 장벽(memory wall)으로 불리는 데이터 병목 현상을 극복하기 위한 목적으로 사용

2. PIM의 아키텍처 및 기술 요소

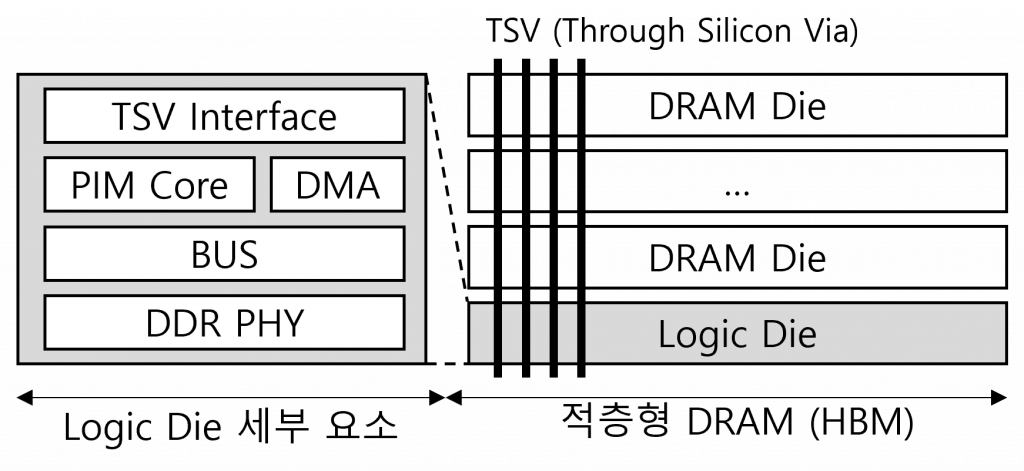

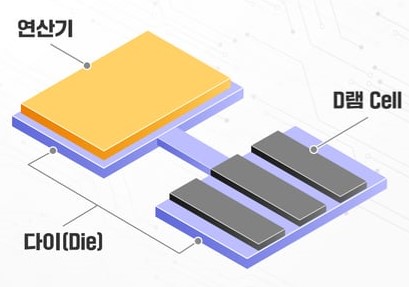

(1) PIM의 아키텍처

|

(2) PIM의 기술 요소

| 구분 | 기술 요소 | 역할 |

|---|---|---|

| Logic Die 내 연산 | TSV Interface | – 전도성 재료를 채운 실리콘 관통 전극 패키징 |

| PIM Core | – DRAM 고속 Access, Data Intensive Processing | |

| DMA | – CPU 개입 없이 기억장치 직접 데이터 전송 | |

| BUS | – 데이터 전송을 위한 장치 간 물리적 연결 | |

| DDR PHY | – Uncacheable Memory Space 기반 PIM Core 연 | |

| 적층형 DRAM (HBM) | DRAM Die | – DRAM Cell 그룹, 패키징 단위 |

| Logic Die | – 다른 칩셋 및 PHY와 DRAM Die 연결 | |

| Micro Bump | – 미세 돌기모양 금속으로 반도체 간 접합 연결 | |

| 기존 연산 장치 | Processing Unit | – CPU, GPU 등 전통적인 컴퓨팅 연산 수행 |

| Memory Controller | – DRAM 등 메모리와 Processing Unit 연결 |

- PIM 기술은 컴퓨팅 성능을 극대화하고 인공지능 연산에 최적화가 가능하지만, 현재 반도체 산업의 기술 성숙도에 따라 PIM 기술을 즉시 적용하기는 어려우며, 중간 단계인 PNM (Processing-near-Memory) 거쳐 발전할 것으로 예상됨

3. PIM과 PNM 비교

| 비교 항목 | PIM (Processing-in-Memory) | PNM (Processing-near-Memory) |

|---|---|---|

| 개념도 |  |  |

| 특징 | 메모리 칩 내 연산기를 탑재하여 데이터 이동 없이 연산 수행 | 메모리 근처 별도의 칩에 연산기를 탑재하여 데이터 이동 최소화 연산 수행 |

| 연산기 위치 | DRAM 칩 내부에 연산기 탑재 | DRAM 근처 별도의 칩(chip)에 배치 |

| 전송 지연 | 메모리 내 연산, 전송 지연 없음 | 연산 시 전송 지연을 최소화 |

| 장점 | 데이터 이동 제거, 병렬처리 극대화 | 범용성 확보, 전력 효율성 향상 |

| 단점 | 특정 연산에 특화되어 변경 어려움 | PIM에 비해 데이터 처리 성능 낮음 |

| 적용 분야 | AI, 빅데이터 실시간 처리 분야 | 고성능 컴퓨팅 및 데이터센터 분야 |

- PIM은 DRAM 칩 내부에 연산기를 탑재하여 데이터 이동 없이 성능을 극대화할 수 있으나, 특정 연산만 사용 가능하도록 만들어지므로 범용성이 낮아 PNM 등 중간 단계를 거쳐야 하므로 지속적인 연구/개발 필요

4. PIM의 한계점 및 대응 방안

| 한계점 | 대응 방안 |

|---|---|

| – 비효율적 면적으로 원가 상승 – 가속기 대비 낮은 컴퓨팅 성능 – 복잡한 프로그래밍 모델 필요 – 특정 연산만 사용(낮은 범용성) | – HBM 기반 저비용으로 효율적 제조 – GPU의 workload를 오프로딩 적용 – GPU 등 가속기와 co-work 기반 보완 – PNM 등 중간 단계를 거쳐 연구/개발 |

- 폭발적으로 증가하는 인공지능 데이터량 처리에 PIM과 같은 효율적인 컴퓨팅 구조가 필요하므로 HBM(High Bandwidth Memory) → PNM(Process Near Memory) → PIM(Process In Memory) → CIM(Computing In Memory) 순서로 발전할 것으로 전망되며, HBM-PIM 또는 가속기-PIM 같은 개선된 컴퓨팅 구조에 대한 지속적인 연구 필요

[참고]

- 전자공학회지, 프로세싱-인-메모리를 위한 메모리 소자 기술

- SK하이닉스, 메모리의 연산, 차세대 지능형 메모리 PIM과 PNM의 등장

- 삼성전자, 차세대 AI를 위한 첨단 메모리 기술 공개