2019년 1월 31일

뉴로모픽칩 (Neuromorphic chip)

I. 시냅스를 모방한 저전력 컴퓨팅, 뉴로모픽칩

가. 뉴로모픽칩의 개념

- 인간 뇌의 뉴런-시냅스 구조를 모방하여 연산, 저장, 통신 기능을 융합한 다수의 저전력 코어 기반 칩

나. 뉴로모픽칩의 목적

| 연산, 저장, 통신 기능 융합 | – 폰-노이만 구조의 CPU-메모리 방식 탈피하여 연산/저장/통신 기능 융합 |

| 뉴런 기반 인공지능 연산 | – 인간 뇌의 뉴런을 모방하여 출력 데이터를 입력으로 받아 딥러닝 학습 수행 |

II. 뉴로모픽칩 구조 및 메커니즘

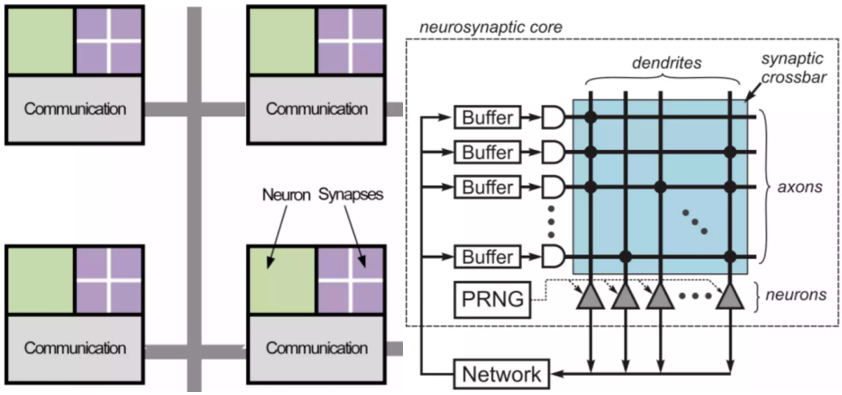

가. 뉴로모픽칩 구조

|

- 뉴런-시냅스 구조로 연산/저장/통신 기능 융합 병목현상 제거

나. 뉴로모픽칩 구성요소

| 구분 | 구성요소 | 핵심 기능 |

|---|---|---|

| 시냅틱 코어 | 입력 뉴런 | – axon, 이전코어에서 신호 수신 |

| 출력 뉴런 | – dendrite, 다음코어로 신호 전달 | |

| 시냅틱 크로스 | – synapse, 입력과 출력 뉴런 연결 | |

| 처리 신호 | weight | – 출력→입력 신호 전달 활성화 |

| spike | – 뉴런 통해 전달되는 임계 전압 | |

| PRNG | – 뉴런에 대한 의사 난수 가중치 |

- 시냅틱 코어는 학습을 통해 시냅틱 크로스를 활성/비활성화 시켜, spike 전달 여부를 결정

다. 뉴로모픽칩 동작 메커니즘

| 개념도 | 설명 |

|---|---|

| – 한 코어에서 발생한 전기 신호는 다음 코어로 빠르게 전달되며, 둘 사이 연관이 높으면 저항을 낮추어 전류량을 자동으로 늘림 |

- 뉴로모픽칩은 독립적 인공지능이 필요한 로봇, 자율주행 등 여러 분야의 핵심 기술로 국내외 기술개발 경쟁 중

III. 뉴로모픽 컴퓨팅과 기존 컴퓨팅의 차이점

| 항목 | 뉴로모픽 컴퓨팅 | 기존 컴퓨팅 |

|---|---|---|

| 구성 | 뉴런, 시냅스(병렬식) | CPU, RAM, I/O(직렬식) |

| 처리 데이터 | 디지털, 아날로그 | 디지털 |

| 처리 방식 | 병렬 처리 | 순차 처리 |

| 기본 소자 | 뉴런 | 논리 소자 |

| 실행 근거 | 학습 | 사전 프로그래밍 |

| 정보 저장 | 뉴런 간 연결강도 | 기억장치(RAM) |

| 특징 | 낮은소모전력,학습 | 뛰어난 연산 능력 |

| 응용분야 | 연상, 추론, 인식 | 복잡한 계산 |

- 뉴로모픽칩 중 트루노스의 경우 28나노 파운드리 공정기반 고성능 저전력 설계로 인공지능 연산에 사용